# Low Power High Speed Carry Select Adder Using GDI-MUX

Ajin Assistant Professor/ECE, Prathyusha Engineering College, India.

Dr.S.Hemajothi Professor/ECE, Prathyusha Engineering College, India.

Darwin Assistant Professor -II/ECE, Prathyusha Engineering College, India.

Dr.L.Vanitha Associate Professor/ECE, Prathyusha Engineering College, India.

S.Shirley Helen Judith M.E., Student, Panimalar Engineering College, India.

Abstract – This paper discusses about the performance characteristics of a Full Adder based Carry Select Adder using various logics and also GDI-MUX technique. The adders are used in many data path applications and also the area, power consumption and delay in the design can be reduced. The proposed technique is the GDI-Mux which enables the reduction of above mentioned parameters and also reduce the number of transistors. The Full Adder based Carry Select Adder designed in Complementary Pass Transistor Logic, Complementary Metal Oxide Semiconductor Logic and Gate Diffusion Input – Mux and they are compared and the most efficient technique is identified.

Index Terms – GDI Technique, Design of carry select adder for low power and high speed VLSI applications.

### 1. INTRODUCTION

The history of transistor dates back to the mid1920s when devices to control current in solid-state diodes and convert them into triodes were attempted to be invented .Very-Large-Scale-Integration(VLSI) is the process of creating an Integrated Circuit by combining thousands of transistors into a single chip. Before the introduction of VLSI IC's had only a limited set of functions they could perform. A well established domain in VLSI is low power design. It has undergone many changes through transistor sizing, clock gating, voltage scaling and so on. For many designs, power dissipation is as important as timing. Requirements for lower power consumption continue to increase significantly as components become battery-powered, smaller and require more functionality. Now a day's power is the primary concerned due to the remarkable growth and success in the field of personal computing devices and wireless communication system which demand high speed computation and complex functionality with low power consumption. The motivations for reducing power consumption differ application to application. The need for lower power systems is being driven by many market segments. The software used is DSCH and MICROWIND.

#### 2. CARRY SELECT ADDER

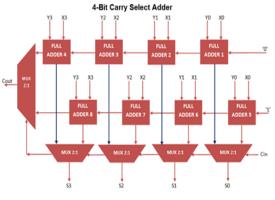

Carry Select Adder is one of the fast adders. It reduces the propagation and can perform fast additions. A 4-bit Carry Selecy Adder is desinged using two Ripple Carry Adders and Multiplexers. The first 4-bit Ripple Carry Adder has "Zero" carry-in and the second 4-bit Ripple Carry Adder has "One" carry-in.

Fig. 1 Carry Select Adder

Four Multiplexers are used to determine the sum output of the Carry Select Adder and One Multiplexer to determine the Carry-out output. The Selection line to the Multiplexer is Cin. The block diagram of a Carry Select Adder is

## 3. PROPOSED TECHNIQUE

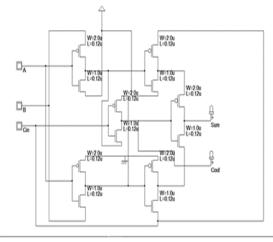

The Gate Diffusion Input (GDI) technique offers realization of extensive variety of logic functions using simple two transistor based circuit arrangement. This scheme is appropriate for fast and low power circuit design, which reduces number of MOS transistors as compared to CMOS and other existing low power techniques, while the logic level swing and static power dissipation improves.

Fig. 2. 2\*1 MUX using GDI

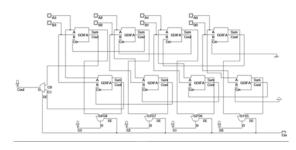

The Carry Select Adder is designed using a Full Adder in CMOS,CPL and GDI-MUX techniques. 28,20,12 transistors are required to design a Full Adder in CMOS,CPL and GDI-MUX technique.The proposed technique is the GDI-MUX technique . The circiut of a Full Adder in GDI-MUX is

Fig. 3 GDI-MUX-Full Adder

A Full Adder has three inputs and two outputs. The inputs are A,B and Cin and the outputs are Sum and Cout. In GDI-MUX Full adder the Cout is obtained as A ANDING B if Cin is "0" and Cout is obtained as A ORING B if Cin is "1". Also the Sum is obtained as A ORING B ORING CIN if the Cout is "0" and Sum is obtained as A ANDING B ANDING Cin if Cout is "1". The above circuit is desinged in DSCH and made into a module which is further used in the design of the Carry Select Adder. The Carry Select Adder in GDI-MUX is

Fig. 4 Layout of CMOS carry select adder

Fig.5 Layout of CPL-Carry Select Adder

## 5. ANALYSIS

The design of Carry Select Adder in CMOS, CPL and GDI-MUX technique is simulated in MICROWIND software to obtain the delay and power consumptions of the respective circuits. Also the number of transistors, Area are compared and tabulated as follows

| Logics       | Techn<br>ology | #. Tr | Power        | Area          | Delay       |

|--------------|----------------|-------|--------------|---------------|-------------|

|              | 90nm           | 264   | 16.815μ<br>W |               |             |

| CMOS<br>-CSA |                |       |              | 3059.7<br>μm² | 1.16<br>Ns  |

|              | 90nm           | 180   | 43.573μ<br>W |               |             |

| CPL-<br>CSA  |                |       |              | 4729.5<br>μm² | 0.916<br>ns |

| GDI-<br>MUX-<br>CSA 2161.5μ 0.493<br>m <sup>2</sup> ns |   | 90nm | 106 | 9.24µW |  |

|--------------------------------------------------------|---|------|-----|--------|--|

| CSA                                                    | - |      |     |        |  |

TABLE.1 PARAMETRIC ANALYSIS

6. CONCLUSION

From the comparison table, it seen that the GDI-MUX technique uses less number of Transistors which in turn reduces the power consumption due to reduced area. The complexity of the circuit is also reduced . Thus the proposed technique is an effective technique.

#### REFERENCES

- [1] Haseeb Pasha, Sangeeta Mangesh, "Study On Various Gdi Techniques For Low Power, High Speed Full Adder Design", IJIREEICE, Vol. 4, Issue. 8, August 2016, pp. 43-48.

- [2] 1, B. Jyothi, K. Vamshi Krishna, M. Basha, "A High Speed Low Power Full Adder Using Gdi Multiplexer", Vol. 3, Issue 9, September 2016

- [3] Padma Devi, Ashima Giridher, Balwinder Singh, "Improved Carry Select Adder With Reduced Area and low Power Consumption, Vol.3, No.4, June 2010, pp 14-18.

- Laxman shanigarapu, bhavanap.Shrivastava, " Low-Power And High [4] Speed Carry Select Adder", Int. Journal of Scientific and Research Publications, Vol.3, Issue 8, August 2013.

- [5] Poojaverma, Rachnamanchanda,"Review Of Various Gdi Techniques For Low Power Digital Circuits", IJETAE, Vol.4, Issue.2, February 2014, pp 387-390.

- [6] Poojaverma, Rachnamanchanda, "Design Of High Speed Carry Select Adder Using Brent Kung Adder", Int. Conference on Electrical, Electronics and Optimization Techniques

- Biswarup mukherjee, "Design & Study Of A Low Power High Speed Full Adder Using GDI Multiplexer", Conference Proceedings. [7]

#### Authors

Mr.Ajin received his B.E., degree from Thangavelu Engineering College and M.E., degree from KCG college of Technology. Presently he is working as an Assistant Professor at Prathyusha Engineering College. He has 5 Research papers in his credit in the Conferences and the Journals.He is having more than 8 years of teaching experience. His area of interest includes VLSI Design, VLSI signal Processing and Digital Systems design.

Dr.S.Hemajothi received her B.E., degree in Electronics & Communication Engineering from Mepco Schlenk Engineering College, Sivakasi in 1993, M.E., degree in Medical Electronics from Anna University, Chennai in 2017 and Ph.D degree from St.Peter's University, Chennai . Presently, she is working as a Professor at Prathyusha Engineering College, Chennai. She is having more than 24 years of teaching experience. She has more than 30 research papers in her credit in National and

International Conferences and Journals, Chennai. Her area of interest includes Bio-Signal processing, Soft computing, Neural Network, Fuzzy Logic and Medical image processing. She is a life member of ISTE & IETE Professonal body.

Mr.Darwin received his B.E., degree in Electronics & Communication Engineering from CSI Institute of Technology M.E., degree from Sri Ram Engineering College, chennai. Presently, he is working as Assistant Professor-II at Prathyusha Engineering College, Chennai. He is having more than 14 years of teaching experience. He has 4 research papers in his r credit in National and International Conferences and Journals, Chennai. His area of interest includes VLSI signal processing, Antennas and wave Propagation, RF &

Microwave Engineering and Microprocessors & Microcontrollers.

Dr.L.Vanitha received her B.E., degree in Electronics & Communication Engineering from Shri Angalamman College Of Engineering and Technology in 1995, M.E., degree in ECE from Sri College Venkateswara Of Engineering (Autonomous) 2010 and Ph.D degree from Anna University, Chennai . Presently, she is working as an Associate Professor at Prathyusha Engineering College, Chennai. She is having more than 24 years of teaching experience. She has more than 30 research papers in her credit in National and International Conferences and Journals, Chennai.

Her area of interest includes Bio-Signal processing, Soft computing, Neural Network, Fuzzy Logic and Medical image processing.

Ms.Shirley Helen Judith received her B.E., degree in Electronics & Communication Engineering from Prathyusha Engineering College in 2017 and doing M.E.,(Communication Systems) in Panimalar Engineering College, Chennai . She is well versed in designing antenna using ADS software. Her area of interest includes Communication, Antennas and wave Propagation.